Al0.44Ga0.56N spacer layer to prevent electron accumulation inside barriers in lattice-matched InAIN/AlGaN/AIN/GaN heterostructures

M. Akazawa, B. Gao, T. Hashizume, M. Hiroki, S. Yamahata et al.

**Applied Physics**

Letters

Citation: Appl. Phys. Lett. **98**, 142117 (2011); doi: 10.1063/1.3578449 View online: http://dx.doi.org/10.1063/1.3578449 View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v98/i14 Published by the American Institute of Physics.

## **Related Articles**

Surface potential analysis of AIN/GaN heterostructures by electrochemical capacitance-voltage measurements J. Appl. Phys. 112, 074508 (2012)

Monolithic integration of high electron mobility InAs-based heterostructure on exact (001) Silicon using a GaSb/GaP accommodation layer Appl. Phys. Lett. 101, 142111 (2012)

The influence of radial heterostructuring on carrier dynamics in gallium nitride nanowires Appl. Phys. Lett. 101, 143104 (2012)

Nondestructive measurement of the minority carrier diffusion length in InP/InGaAs/InP double heterostructures Appl. Phys. Lett. 101, 133501 (2012)

Influence of AlGaN barrier thickness on electrical and device properties in Al0.14Ga0.86N/GaN high electron mobility transistor structures J. Appl. Phys. 112, 053718 (2012)

## Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/ Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded Information for Authors: http://apl.aip.org/authors

## ADVERTISEMENT

## Al<sub>0.44</sub>Ga<sub>0.56</sub>N spacer layer to prevent electron accumulation inside barriers in lattice-matched InAIN/AIGaN/AIN/GaN heterostructures

M. Akazawa,<sup>1,2,a)</sup> B. Gao,<sup>1</sup> T. Hashizume,<sup>1,2</sup> M. Hiroki,<sup>3</sup> S. Yamahata,<sup>3</sup> and N. Shigekawa<sup>3</sup>

<sup>1</sup>Research Center for Integrated Quantum Electronics, Hokkaido University, Sapporo 060-8628, Japan <sup>2</sup>JST–CREST, Sanbancho, Chiyoda-ku, Tokyo 102-0075, Japan

<sup>3</sup>NTT Photonics Laboratories, NTT Corporation, Atsugi, Kanagawa 243-0198, Japan

(Received 13 February 2011; accepted 23 March 2011; published online 7 April 2011)

The barrier structure in lattice-matched InAlN/GaN heterostructures with AlGaN-based spacer layers grown by metal organic vapor phase epitaxy was studied by the capacitance-voltage (C-V) method. To investigate the characteristics under positive bias, an  $Al_2O_3$  overlayer was added. The C-V characteristic of a sample with an  $Al_{0.38}Ga_{0.62}N$  (5 nm)/AlN (0.75 nm) double spacer layer exhibited an anomalous saturation at a value far below the insulator capacitance under positive bias, which indicated electron accumulation at the InAlN/AlGaN interface. The C-V characteristic of an alternative sample with a single  $Al_{0.44}Ga_{0.56}N$  (1.5 nm) spacer layer did not exhibit the anomalous saturation. © 2011 American Institute of Physics. [doi:10.1063/1.3578449]

A lattice-matched InAlN/GaN heterostructure provides a high-density two-dimensional electron gas (2DEG) due to the difference in spontaneous polarization at the interface without any doping.<sup>1,2</sup> To enhance electron mobility, an AlN ultrathin layer has been used as a conventional spacer layer.<sup>3,4</sup> Several reports have been published on the application of the InAlN/AlN/GaN structure to field-effect transistors (FETs) (Refs. 3–5) including normally off type FETs.<sup>5</sup> A recent study, however, reported that the insertion of an Al<sub>0.38</sub>Ga<sub>0.62</sub>N/AlN double spacer layer improved surface flatness and electron mobility compared with those for a single AlN spacer layer.<sup>6</sup> Since the band gap of an Al<sub>0.38</sub>Ga<sub>0.62</sub>N layer is smaller than that of a lattice-matched InAlN layer, electron accumulation might occur at the InAlN/AlGaN interface under positive bias, resulting in a reduction in the effective barrier thickness. Schottky barrier diodes are not suitable for investigating electron accumulation in the barrier layer under positive bias. One of the methods of clarifying electron accumulation inside the barrier layer is to measure capacitance-voltage (C-V) characteristics using samples with an insulator overlayer on the heterostructure. In this letter, the Al<sub>0.38</sub>Ga<sub>0.62</sub>N/AlN double spacer layer is reappraised. A sample with an Al<sub>0.44</sub>Ga<sub>0.56</sub>N single spacer layer is also investigated as an alternative structure, for preventing electron accumulation inside the barrier layer.

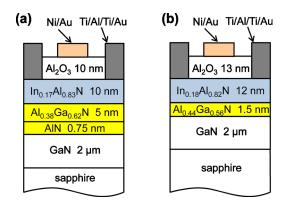

Figure 1 shows the structures of the test samples. An Al<sub>2</sub>O<sub>3</sub> (10 nm)/In<sub>0.17</sub>Al<sub>0.83</sub>N (10 nm)/Al<sub>0.38</sub>Ga<sub>0.62</sub>N (5 nm)/ AlN (0.75 nm)/GaN (2  $\mu$ m) structure and an Al<sub>2</sub>O<sub>3</sub> (13 nm)/In<sub>0.18</sub>Al<sub>0.82</sub>N (12 nm)/Al<sub>0.44</sub>Ga<sub>0.56</sub>N (1.5 nm)/GaN (2  $\mu$ m) structure were fabricated and tested. The fabrication process of the test samples was as follows. Heterostructures were grown by metal organic vapor phase epitaxy. For the cap-annealing process to form an Ohmic contact, a 20 nm thick SiN<sub>x</sub> layer was deposited by electron-cyclotron resonance chemical vapor deposition using a SiH<sub>4</sub>/Ar and N<sub>2</sub> gas mixture at 260 °C. After opening a ring-shaped window by lithography and wet etching using buffered hydrofluoric acid (BHF, HF:NH<sub>4</sub>F=1:5) solution, a ring-shaped Ti/Al/Ti/Au (30 nm/50 nm/20 nm/100 nm) Ohmic electrode was formed. Then the samples were annealed in N<sub>2</sub> ambient at 800 °C for 1 min. After removing the SiN<sub>x</sub> layer using BHF solution, an Al<sub>2</sub>O<sub>3</sub> overlayer was deposited by atomic layer deposition (ALD) at a substrate temperature of 250 °C. Finally, a circular Ni/Au (20 nm/50 nm) electrode was formed in the center of the Ohmic ring.

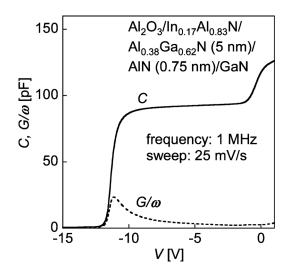

The Hall measurement showed that the In<sub>0.17</sub>Al<sub>0.83</sub>N  $(10\ nm)/Al_{0.38}Ga_{0.62}N$  (5 nm)/AlN (0.75 nm)/GaN heterostructure in Fig. 1(a) produced a 2DEG with a sheet carrier density,  $n_{\rm S}$ , of  $2.2 \times 10^{13}$  cm<sup>-2</sup> and an electron mobility,  $\mu$ , of 1400 cm<sup>2</sup>/V/s, reproducing the previously reported results.<sup>6</sup> The obtained C-V characteristic for the  $Al_2O_3/$ In<sub>0.17</sub>Al<sub>0.83</sub>N/Al<sub>0.38</sub>Ga<sub>0.62</sub>N/AlN/GaN structure is plotted in Fig. 2. A step at approximately 0 V can be seen in the C-V curve in addition to the usual step at approximately -11.5 V, indicating the depletion of the 2DEG. From the capacitance values, the plateau at the negative bias corresponds to electron accumulation at the AlN/GaN interface. Even though the positive bias range was limited due to the leakage through the Al<sub>2</sub>O<sub>3</sub> layer, the capacitance step at 0 V tends to saturate at a value much lower than the insulator capacitance, C<sub>i</sub>, of approximately 260 pF. The saturation capacitance corresponds to the value for electron accumulation at

FIG. 1. (Color online) Schematic sample structures.

0003-6951/2011/98(14)/142117/3/\$30.00

FIG. 2. Measured C-V curve for the Al<sub>2</sub>O<sub>3</sub> (10 nm)/In<sub>0.17</sub>Al<sub>0.83</sub>N (10 nm)/Al<sub>0.38</sub>Ga<sub>0.62</sub>N (5 nm)/AlN (0.75 nm)/GaN structure.  $C_i$  was estimated to be ~260 pF. The bias voltage was swept from the positive side to the negative side at a sweep rate of 25 mV/s.

the InAlN/AlGaN interface. This phenomenon may become a drawback of the heterostructure if it is applied to an FET gate, resulting in parallel conduction and a complicated change in potential.

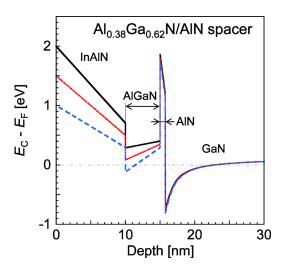

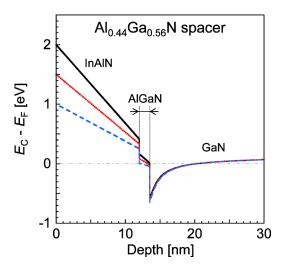

Figure 3 shows conduction band,  $E_{\rm C}$ , potential profiles with respect to the Fermi level,  $E_{\rm F}$ , calculated for the  $In_{0.17}Al_{0.83}N/Al_{0.38}Ga_{0.62}N/AlN/GaN \quad heterostructure \quad by$ the Poisson and solving Schrödinger equations self-consistently<sup>7</sup> for several positions of the surface Fermi level,  $E_{\rm F \ surf.}$  The band alignment based on the amphoteric native-defect model<sup>8</sup> and related experimental data<sup>9,10</sup> was assumed in the calculation, while the interface charge due to polarization was estimated in accordance with Ref. 1. For the sample with an Al<sub>0.38</sub>Ga<sub>0.62</sub>N/AlN spacer layer, it can be seen that applying positive bias leads to electron accumulation at the InAlN/AlGaN interface. In the sample with the Al<sub>2</sub>O<sub>3</sub> overlayer, electron accumulation at the InAlN/AlGaN interface is expected to occur before that at the Al<sub>2</sub>O<sub>3</sub>/InAlN interface because  $E_{\rm C}$  for the AlGaN layer is closer to  $E_{\rm F}$  than that for the InAlN layer, which is consistent with the mea-

FIG. 3. (Color online)  $E_{\rm C}$  potential profiles of the In<sub>0.17</sub>Al<sub>0.83</sub>N (10 nm)/Al<sub>0.38</sub>Ga<sub>0.62</sub>N (5 nm)/AlN (0.75 nm)/GaN structure calculated for several  $E_{\rm F~surf}$  positions.

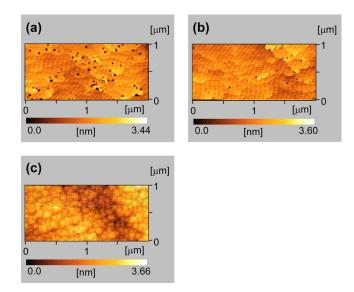

FIG. 4. (Color online) AFM images for (a)  $Al_{0.44}Ga_{0.56}N$  (2.0 nm)/GaN, (b)  $Al_{0.44}Ga_{0.56}N$  (1.5 nm)/GaN, and (c)  $In_{0.18}Al_{0.82}N$  (12 nm)/ $Al_{0.44}Ga_{0.56}N$  (1.5 nm)/GaN.

sured C-V curve. The spacer layer should be thinner with a wider band gap to prevent electron accumulation inside the barrier layer.

An alternative heterostructure was designed as shown in Fig. 1(b). The Al molar fraction, x, of the Al<sub>x</sub>Ga<sub>1-x</sub>N spacer layer was increased to enlarge the band gap. The critical thickness, however, decreases as x increases. The spacer layer should be as thick as possible to obtain a high 2DEG mobility to separate electrons from the bottom of the InAlN layer, even though it should be sufficiently thin to prevent electron accumulation inside the barrier layer. In addition, an excessively high value of x may result in deterioration of the surface flatness. We, therefore, attempted to increase x slightly from x=0.38 to 0.44. The corresponding increase in the conduction band offset relative to GaN was estimated to be about 0.1 eV by the calculation described above.

It was expected that the surface flatness of the InAlN/Al<sub>0.44</sub>Ga<sub>0.56</sub>N/GaN structure could be superior to that of the conventional InAlN/AlN/GaN structure because the lattice mismatch is reduced. To verify this, the surface morphology of the grown heterostructures was investigated using an atomic force microscope (AFM). The results are summarized in Fig. 4. When the thickness of the Al<sub>0,44</sub>Ga<sub>0,56</sub>N layer was greater than 1.5 nm, the number and size of pits increased remarkably as shown in Fig. 4(a) for 2.0 nm thick Al<sub>0.44</sub>Ga<sub>0.56</sub>N on GaN. Therefore, the optimal thickness of the Al<sub>0.44</sub>Ga<sub>0.56</sub>N layer was determined to be 1.5 nm. The surface morphology of 1.5 nm Al<sub>0.44</sub>Ga<sub>0.56</sub>N on GaN shown in Fig. 4(b) was superior to that of an AlN ( $\sim 1 \text{ nm}$ )/GaN surface,<sup>6</sup> which led to a smoother InAlN/AlGaN/GaN surface [root mean square roughness (rms): 0.35 nm], as shown in Fig. 4(c), than that of the conventional InAlN/AlN/GaN (rms: 0.53 nm) structure.<sup>6</sup> The Hall measurement showed that a 2DEG with  $n_{\rm S}=2.1\times10^{13}$  cm<sup>-2</sup> and  $\mu=1100$  cm<sup>2</sup>/ V/s was obtained for the  $In_{0.18}Al_{0.82}N/Al_{0.44}Ga_{0.56}N/GaN$ heterostructure. Although the mobility is lower for the sample with the Al<sub>0.44</sub>Ga<sub>0.56</sub>N single spacer layer, it is much higher than the typical value of less than 200  $\text{cm}^2/\text{V/s}$  for an InAlN/GaN structure without a spacer layer.<sup>4,6</sup>

FIG. 5. (Color online)  $E_{\rm C}$  potential profiles of the In<sub>0.18</sub>Al<sub>0.82</sub>N (12 nm)/Al<sub>0.44</sub>Ga<sub>0.56</sub>N (1.5 nm)/GaN structure calculated for several  $E_{\rm F}$  surf positions.

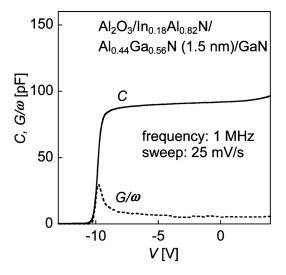

A calculation employing the same method used for Fig. 3 showed that InAlN (12 nm)/Al<sub>0.44</sub>Ga<sub>0.56</sub>N (1.5 nm) should operate normally as a barrier under positive bias as shown in Fig. 5. Actually, the measured C-V characteristic of the Al<sub>2</sub>O<sub>3</sub>/In<sub>0.18</sub>Al<sub>0.82</sub>N/Al<sub>0.44</sub>Ga<sub>0.56</sub>N/GaN structure exhibited a wide plateau as plotted in Fig. 6. The measured capacitance at approximately -3 V had a value corresponding to the electron accumulation at the Al<sub>0.44</sub>Ga<sub>0.56</sub>N/GaN interface

FIG. 6. Measured C-V curve for the Al<sub>2</sub>O<sub>3</sub> (13 nm)/In<sub>0.18</sub>Al<sub>0.82</sub>N (12 nm)/Al<sub>0.44</sub>Ga<sub>0.56</sub>N (1.5 nm)/GaN structure.  $C_i$  was estimated to be ~190 pF. The bias voltage was swept from the positive side to the negative side at a sweep rate of 25 mV/s.

and slightly increased as the bias increased toward the onset of electron accumulation at the InAlN surface at approximately 4 V. The positive bias limit of this sample, due to the leakage through the  $Al_2O_3$  layer, was higher than that of the sample with the  $Al_{0.38}Ga_{0.62}N/AlN$  double spacer layer in Fig. 2. Since the  $Al_2O_3$  layer was as thin as 10 nm, its resistivity should have been affected by the roughness and native oxide components of the InAlN surface before the deposition. The pretreatment, using the BHF solution to remove the  $SiN_x$  layer, followed by the sample transfer in air to the ALD chamber was not optimized completely for the InAlN surface, which possibly resulted in the difference of the insulator quality between two samples.

In summary,  $Al_2O_3$  (10 nm)/ $In_{0.17}Al_{0.83}N$  (10 nm)/ Al<sub>0.38</sub>Ga<sub>0.62</sub>N (5 nm)/AlN (0.75 nm)/GaN and Al<sub>2</sub>O<sub>3</sub> (13 nm)/In<sub>0.18</sub>Al<sub>0.82</sub>N (12 nm)/Al<sub>0.44</sub>Ga<sub>0.56</sub>N (1.5 nm)/GaN structures were fabricated and studied. The C-V characteristic of the former structure exhibited an anomalous saturation at a value far below the insulator capacitance under positive bias, indicating electron accumulation at the InAlN/AlGaN interface, while no such saturation was observed in the latter structure. The InAlN/Al<sub>0.44</sub>Ga<sub>0.56</sub>N (1.5 nm)/GaN structure showed improved surface flatness compared with the conventional InAlN/AlN/GaN structure. A 2DEG with  $n_{\rm S}$ =2.1  $\times 10^{13}$  cm<sup>-2</sup> and  $\mu$ =1100 cm<sup>2</sup>/V/s was obtained by using the Al<sub>0.44</sub>Ga<sub>0.56</sub>N single spacer layer. Since thinning the barrier layer is one of the ways of achieving a normally off FET,<sup>5</sup> the InAlN/Al<sub>0.44</sub>Ga<sub>0.56</sub>N (1.5 nm)/GaN structure with a thin spacer layer is advantageous from this viewpoint.

- <sup>1</sup>O. Ambacher, R. Dimitrov, M. Stutzmann, B. E. Foutz, M. J. Murphy, J. A. Smart, J. R. Shealy, N. G. Weimann, K. Chu, M. Chumbes, B. Green, A. J. Sierakowski, W. J. Schaff, and L. F. Eastman, Phys. Status Solidi B **216**, 381 (1999).

- <sup>2</sup>J. Kuzmík, IEEE Electron Device Lett. **22**, 510 (2001).

- <sup>3</sup>M. Higashiwaki and T. Matsui, Jpn. J. Appl. Phys., Part 2 43, L768 (2004).

- <sup>4</sup>M. Gonschorek, J.-F. Carlin, E. Feltin, M. A. Py, and N. Grandjean, Appl. Phys. Lett. **89**, 062106 (2006).

- <sup>5</sup>C. Ostermaier, G. Pozzovivo, J.-F. Carlin, B. Basnar, W. Schrenk, Y. Douvry, C. Gaquière, J.-C. DeJaeger, K. Čičo, K. Fröhlich, M. Gonschorek, N. Grandjean, G. Strasser, D. Pogany, and J. Kuzmík, IEEE Electron Device Lett. **30**, 1030 (2009).

- <sup>6</sup>M. Hiroki, N. Maeda, and T. Kobayashi, Appl. Phys. Express **1**, 111102 (2008).

- <sup>7</sup>ID Poisson–Schrodinger solver program developed by Prof Gregory Snider, University of Notre Dame, http://www.nd.edu/~gsnider/.

- <sup>8</sup>W. Walukiewicz, S. X. Li, J. Wu, K. M. Yu, J. W. Ager III, E. E. Haller, H. Lu, and W. J. Schaff, J. Cryst. Growth **269**, 119 (2004).

- <sup>9</sup>R. E. Jones, R. Broesler, K. M. Yu, J. W. Ager III, E. E. Haller, W. Walukiewicz, X. Chen, and W. J. Schaff, J. Appl. Phys. **104**, 123501 (2008).

- <sup>10</sup>T. Kubo, H. Taketomi, H. Miyake, K. Hiramatsu, and T. Hashizume, Appl. Phys. Express 3, 021004 (2010).